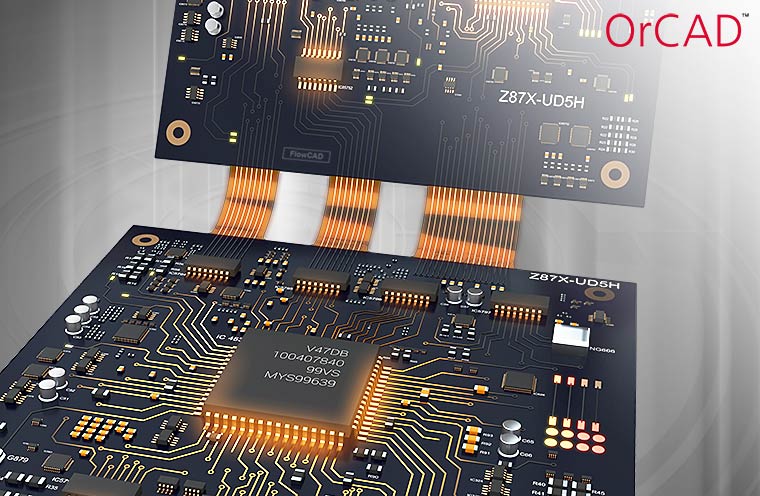

OrCAD PCB Design

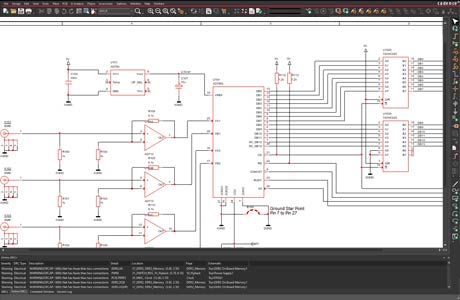

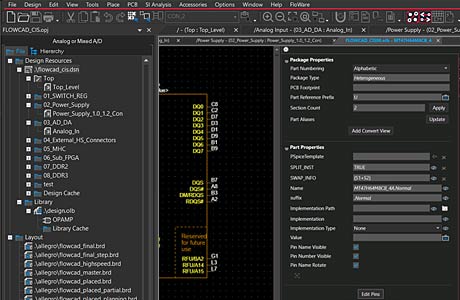

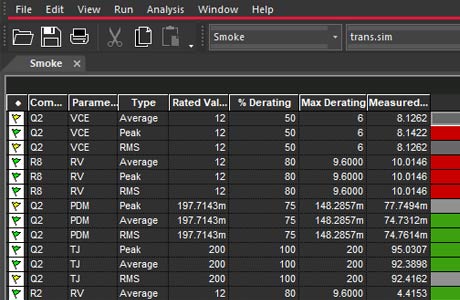

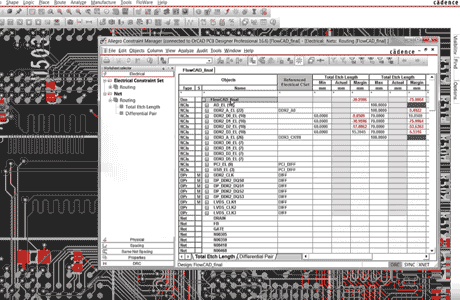

OrCAD ist eine Software-Produktfamilie für professionelles PCB Design, Leiterplattenlayout, Simulation und Routing. OrCAD PCB Editor basiert auf der Cadence Allegro Engine und bietet Ihnen schnelle und vorhersehbare Ergebnisse. OrCAD kann in einer Entwurfsmethodik getriebenen durch Einschränkungen verwendet werden, bei der die Designregeln im Constraint Manager verwaltet werden. Diese Regeln werden bei der Eingabe in den Schaltplan erfasst und in Echtzeit als Design Rule Checks (DRC) überprüft.

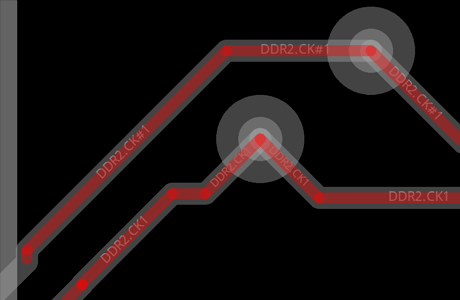

PCB Layout und Hochgeschwindigkeits-Routing werden durch eine Vielzahl von Automatisierungen unterstützt, was Ihr Design sehr effizient und zuverlässig macht. Mit OrCAD können Sie ein fertigungsgerechtes Leiterplattendesign schneller erstellen.

OrCAD ist ein seit Jahren bekanntes Tool, so dass ein komplettes Ökosystem mit Referenzdesigns, schematischen Symbolen, PCB Footprints, Komponenteninformationen, Apps und TCL-Erweiterungen in der Designer Community verfügbar ist.